Rana računala bila su potpuno sekvencijalna. Svaka instrukcija koju je procesor primio trebala je biti dovršena u cijelosti prije nego što se mogla pokrenuti sljedeća. Postoji pet faza za većinu instrukcija: dohvaćanje instrukcija, dekodiranje instrukcija, izvršenje, pristup memoriji i povratni upis. Odnosno, ove faze dobivaju upute koje treba dovršiti, odvajajući operaciju od vrijednosti operiran, izvršiti operaciju, otvoriti registar u koji će biti upisan rezultat i upisati rezultat u otvoreni Registar.

Svaka od ovih faza treba završiti jedan ciklus. Nažalost, ako podaci nisu u registru, moraju se zatražiti iz predmemorije CPU-a ili RAM-a sustava. Ovo je puno sporije, dodaje desetke ili stotine ciklusa takta latencije. U međuvremenu, sve ostalo treba pričekati jer se drugi podaci ili upute ne mogu obraditi. Ovaj tip dizajna procesora naziva se subskalarnim jer izvodi manje od jedne instrukcije po taktu.

Cjevovodno povezivanje na skalar

Skalarni procesor može se postići primjenom cjevovoda sustava. Svaka od pet faza instrukcije koja se izvršava izvodi se u različitim dijelovima hardvera u stvarnoj jezgri procesora. Dakle, ako ste pažljivi s podacima koje unosite u hardver za svaku fazu, svaki od njih možete zauzeti svaki ciklus. U savršenom svijetu, to bi moglo dovesti do 5x ubrzanja i da procesor bude savršeno skalaran, izvršavajući punu instrukciju po ciklusu.

U stvarnosti su programi složeni i smanjuju propusnost. Na primjer, ako imate dvije instrukcije zbrajanja "a = b + c" i "d = e + f", one se mogu pokrenuti u cjevovodu bez problema. Međutim, ako imate "a = b + c" nakon čega slijedi "d = a + e", imate problem. Pod pretpostavkom da su ove dvije upute neposredno jedna iza druge, postupak izračuna nove vrijednosti "a" neće biti dovršen, a kamoli da se zapiše natrag u memoriju prije nego što druga instrukcija pročita staru vrijednost "a" i zatim da pogrešan odgovor za "d".

Ovom se ponašanju može suprotstaviti uključivanjem dispečera koji analizira nadolazeće upute i osigurava da se nijedna instrukcija koja ovisi o drugoj ne izvodi u pretijesnom nizu. Zapravo pokreće program pogrešnim redoslijedom kako bi to popravio. Ovo funkcionira jer se mnoge upute ne oslanjaju nužno na rezultate prethodnih.

Proširenje cjevovoda na superskalar

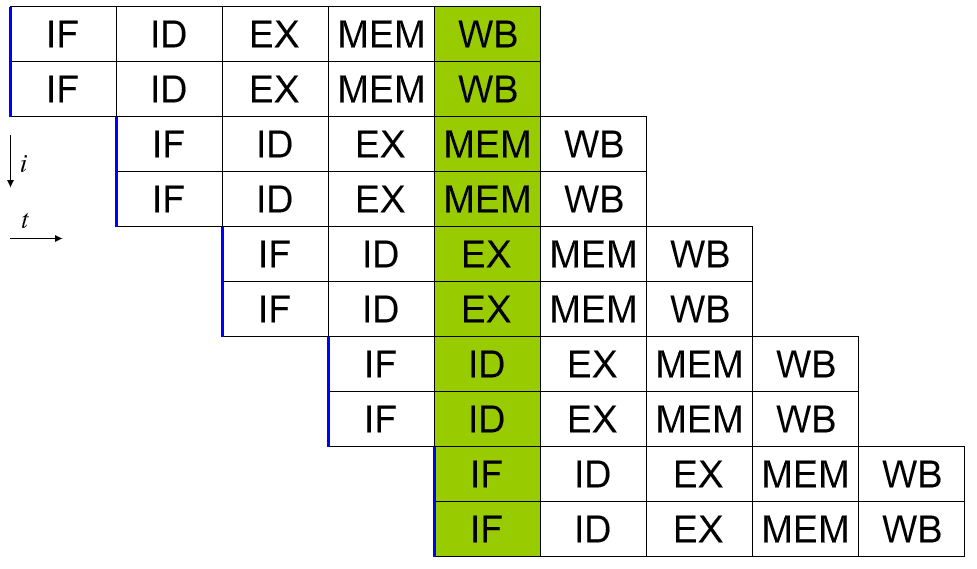

Superskalarni procesor može izvoditi više od jedne pune instrukcije po ciklusu. Jedan od načina da se to učini je proširenje cjevovoda tako da postoje dva ili više dijelova hardvera koji mogu podnijeti svaku fazu. Na taj način dvije instrukcije mogu biti u svakoj fazi cjevovoda u svakom ciklusu. To očito rezultira povećanom složenošću dizajna jer se hardver duplicira, no nudi izvrsne mogućnosti skaliranja performansi.

Međutim, povećanje performansi povećanjem cjevovoda za sada je samo učinkovito. Toplinska ograničenja i ograničenja veličine postavljaju neka ograničenja. Postoje i značajne komplikacije u rasporedu. Učinkoviti dispečer sada je još kritičniji jer mora osigurati da se niti jedan od dva skupa uputa ne oslanja na rezultat bilo koje od drugih uputa koje se obrađuju.

Prediktor grananja je dio dispečera koji postaje sve kritičniji što je procesor više superskalaran. Neke upute mogu imati dva potencijalna ishoda, od kojih svaki vodi različitim sljedećim uputama. Jednostavan primjer bila bi izjava "ako". “Ako je ovo istina, učini ono, inače ovo drugo”. Prediktor grananja pokušava predvidjeti ishod operacije grananja. Zatim unaprijed planira i izvršava upute slijedeći ono za što vjeruje da je vjerojatni ishod.

Postoji mnogo složene logike u modernim prediktorima grana, što može rezultirati stopama uspješnosti predviđanja grana reda veličine 98%. Točno predviđanje štedi vrijeme koje se moglo izgubiti čekajući stvarni rezultat, netočno predviđanje zahtijeva da se predviđeno upute i bilo koji od njihovih rezultata biti odbačeni, a prave upute pokrenute umjesto njih, što dolazi s malom kaznom u odnosu na samo čekao. Stoga visoke stope uspjeha predviđanja mogu značajno povećati učinak.

Zaključak

Računalni procesor se smatra superskalarnim ako može izvesti više od jedne instrukcije po taktu. Rana računala bila su potpuno sekvencijalna, izvršavajući samo jednu instrukciju odjednom. To je značilo da je svakoj instrukciji bilo potrebno više od jednog ciklusa da se izvrši, pa su ti procesori bili subskalarni. Osnovni cjevovod koji omogućuje korištenje hardvera specifičnog za svaki stupanj instrukcije može izvršiti najviše jednu instrukciju po ciklusu takta, što ga čini skalarnim.

Treba napomenuti da niti jedna pojedinačna instrukcija nije u potpunosti obrađena u jednom taktu. I dalje je potrebno najmanje pet ciklusa. Međutim, više uputa može biti u cjevovodu odjednom. To omogućuje protok jedne ili više dovršenih instrukcija po ciklusu.

Superskalar ne treba brkati s hiperskalerom koji se odnosi na tvrtke koje mogu ponuditi računalne resurse hiperskala. Hyperscale computing uključuje mogućnost neprimjetnog skaliranja hardverskih resursa, kao što su računanje, memorija, mrežna propusnost i pohrana, prema zahtjevu. To se obično nalazi u velikim podatkovnim centrima i okruženjima računalstva u oblaku.