Рани рачунари су били потпуно секвенцијални. Свака инструкција коју је процесор добио требало је да буде довршена у потпуности да би се могла покренути следећа. Постоји пет фаза за већину инструкција: преузимање инструкције, декодирање инструкције, извршавање, приступ меморији и повратно уписивање. Односно, ове фазе добијају инструкције које треба завршити, одвојити операцију од вредности које су оперисан, изврши операцију, отвори регистар у који ће бити уписан резултат и уписати резултат у отворени регистровати.

Свака од ових фаза треба да траје један циклус. Нажалост, ако подаци нису у регистру, онда се морају затражити из ЦПУ кеша или системске РАМ меморије. Ово је много спорије, додајући десетине или стотине циклуса латенције. У међувремену, све остало треба да сачека јер се никакви други подаци или упутства не могу обрадити. Овај тип дизајна процесора се назива субскаларним јер изводи мање од једне инструкције по циклусу такта.

Превођење на скалар

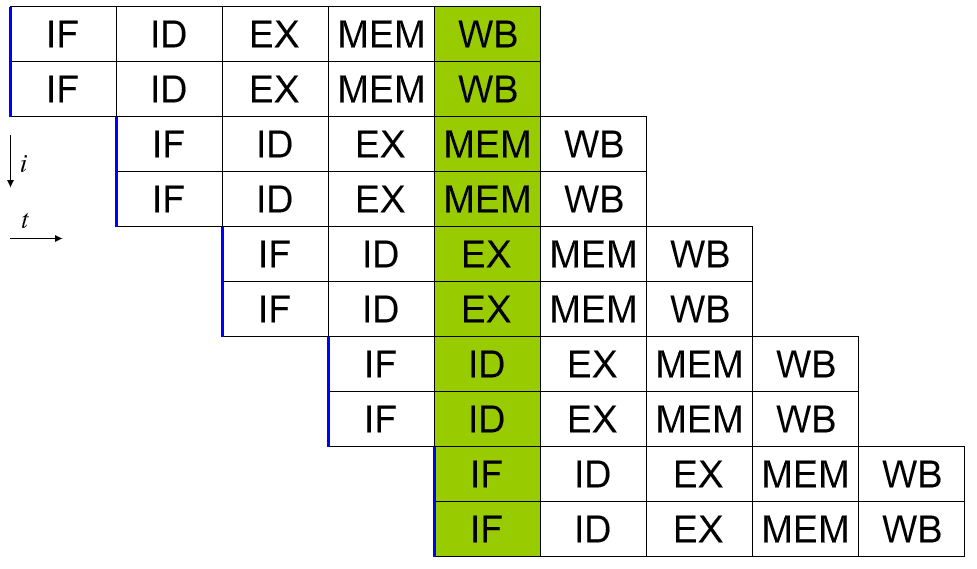

Скаларни процесор се може постићи применом системског цевовода. Свака од пет фаза инструкције која се извршава ради у различитим битовима хардвера у стварном језгру процесора. Стога, ако будете пажљиви са подацима које уносите у хардвер за сваку фазу, сваки од њих можете држати заузетим у сваком циклусу. У савршеном свету, ово би могло да доведе до 5к убрзања и да процесор буде савршено скаларан, извршавајући пуну инструкцију по циклусу.

У стварности, програми су сложени и смањују пропусност. На пример, ако имате две инструкције за сабирање „а = б + ц“ и „д = е + ф“, оне се могу покренути у цевоводу без проблема. Међутим, ако имате „а = б + ц“ праћено „д = а + е“, имате проблем. Под претпоставком да су ове две инструкције директно једна за другом, процес израчунавања нове вредности „а“ неће бити завршен, а камоли да буде записано назад у меморију пре него што друга инструкција прочита стару вредност „а“ и затим да погрешан одговор за “д”.

Овом понашању се може супротставити укључивање диспечера, који анализира предстојеће инструкције и осигурава да се ниједна инструкција која зависи од друге не изводи у сувише блиском низу. Он заправо покреће програм погрешним редоследом да би ово поправио. Ово функционише, јер се многа упутства не ослањају нужно на резултат претходног.

Проширивање цевовода на суперскалар

Суперскаларни процесор је способан да покрене више од једне пуне инструкције по циклусу. Један од начина да се то уради је проширење цевовода тако да постоје два или више битова хардвера који могу да обрађују сваку фазу. На овај начин две инструкције могу бити у свакој фази цевовода у сваком циклусу. Ово очигледно резултира повећаном сложеношћу дизајна јер се хардвер дуплира, међутим, нуди одличне могућности скалирања перформанси.

Међутим, повећање перформанси од повећања цевовода до сада је ефикасно. Термичка ограничења и ограничења постављају нека ограничења. Постоје и значајне компликације у распореду. Ефикасан диспечер је сада још критичнији јер мора да обезбеди да се ниједан од два сета инструкција не ослања на резултат било које друге инструкције која се обрађује.

Предиктор гранања је део диспечера који постаје све критичнији што је процесор више суперскаларни. Нека упутства могу имати два потенцијална исхода, од којих сваки води ка различитим следећим упутствима. Једноставан пример би била изјава „ако“. „Ако је ово истина, уради оно, у супротном уради ово друго“. Предиктор гранања покушава да предвиди исход операције гранања. Затим превентивно заказује и извршава упутства пратећи оно што верује да ће бити вероватан исход.

Постоји много сложене логике у савременим предикторима грана, што може резултирати стопама успешности предвиђања грана од 98%. Исправно предвиђање штеди време које је могло бити изгубљено чекајући стварни резултат, нетачно предвиђање захтева да се предвиђено упутства и било који њихов резултат се одбацују и праве инструкције се извршавају на њиховом месту, што долази са малом казном због само чекао. Тако високе стопе успеха предвиђања могу приметно повећати перформансе.

Закључак

Рачунарски процесор се сматра суперскаларним ако може да изврши више од једне инструкције по циклусу такта. Рани рачунари су били потпуно секвенцијални, извршавајући само једну по једну инструкцију. То је значило да је свакој инструкцији било потребно више од једног циклуса да се заврши и тако су ови процесори били субскаларни. Основни цевовод који омогућава коришћење хардвера специфичног за фазу за сваку фазу инструкције може да изврши највише једну инструкцију по циклусу такта, чинећи је скаларном.

Треба напоменути да ниједна појединачна инструкција није у потпуности обрађена у једном циклусу такта. И даље је потребно најмање пет циклуса. Међутим, више инструкција може бити у припреми одједном. Ово омогућава проток једне или више довршених инструкција по циклусу.

Суперскалар не треба мешати са хиперскалером који се односи на компаније које могу да понуде рачунарске ресурсе хиперскаларности. Хиперсцале рачунарство укључује могућност неприметног скалирања хардверских ресурса, као што су рачунар, меморија, пропусни опсег мреже и складиштење, према захтеву. Ово се обично налази у великим центрима података и окружењима рачунарства у облаку.