Las primeras computadoras eran completamente secuenciales. Cada instrucción que recibía el procesador debía completarse en su totalidad en orden antes de poder iniciar la siguiente. Hay cinco etapas para la mayoría de las instrucciones: obtención de instrucciones, decodificación de instrucciones, ejecución, acceso a la memoria y reescritura. Respectivamente, estas etapas obtienen la instrucción que debe completarse, separan la operación de los valores que se están operado, ejecutar la operación, abrir el registro en el que se escribirá el resultado y escribir el resultado en el Registrarse.

Cada una de estas etapas debe tomar un ciclo para completarse. Desafortunadamente, si los datos no están en un registro, deben solicitarse desde el caché de la CPU o la RAM del sistema. Esto es mucho más lento y agrega docenas o cientos de ciclos de reloj de latencia. Mientras tanto, todo lo demás debe esperar, ya que no se pueden procesar otros datos o instrucciones. Este tipo de diseño de procesador se denomina subescalar, ya que ejecuta menos de una instrucción por ciclo de reloj.

Canalización a escalar

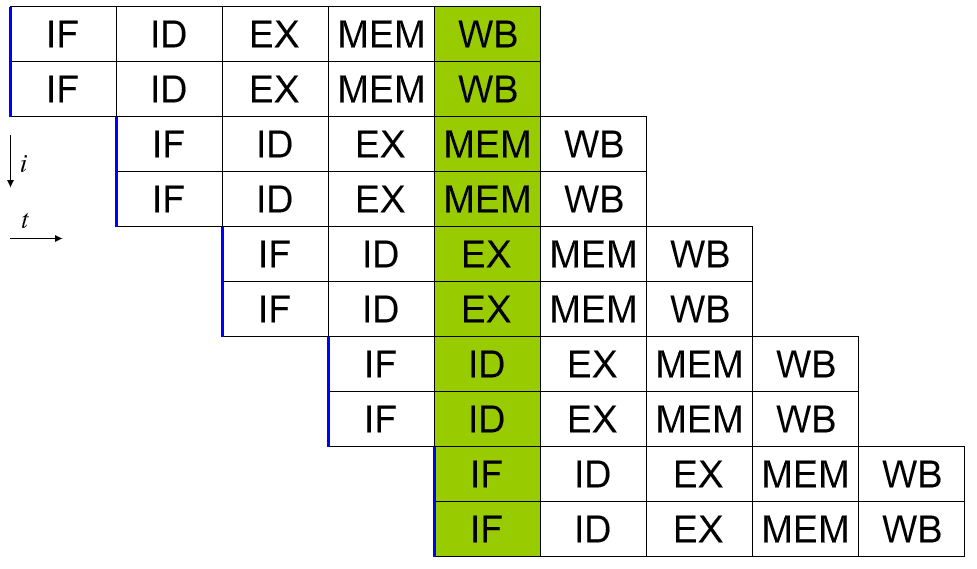

Se puede lograr un procesador escalar aplicando una canalización del sistema. Cada una de las cinco etapas de una instrucción que se ejecuta se ejecuta en diferentes bits de hardware en el núcleo del procesador real. Por lo tanto, si tiene cuidado con los datos que alimenta al hardware para cada etapa, puede mantenerlos ocupados en cada ciclo. En un mundo perfecto, esto podría conducir a una aceleración de 5x y que el procesador sea perfectamente escalar, ejecutando una instrucción completa por ciclo.

En realidad, los programas son complejos y reducen el rendimiento. Por ejemplo, si tiene dos instrucciones de suma "a = b + c" y "d = e + f", estas pueden ejecutarse en una canalización sin problemas. Sin embargo, si tiene "a = b + c" seguido de "d = a + e", tiene un problema. Suponiendo que estas dos instrucciones estén directamente una detrás de la otra, el proceso para calcular el nuevo valor de "a" no se habrá completado, y mucho menos escribirse de nuevo en la memoria antes de que la segunda instrucción lea el valor anterior de "a" y luego dé la respuesta incorrecta para "d".

Este comportamiento se puede contrarrestar con la inclusión de un despachador, que analiza las próximas instrucciones y garantiza que ninguna instrucción que dependa de otra se ejecute en una sucesión demasiado cercana. En realidad, ejecuta el programa en el orden incorrecto para solucionar este problema. Esto funciona, porque muchas instrucciones no dependen necesariamente del resultado de una anterior.

Expansión de la canalización a superescalar

Un procesador superescalar es capaz de ejecutar más de una instrucción completa por ciclo. Una forma de hacer esto es expandir la canalización para que haya dos o más partes de hardware que puedan manejar cada etapa. De esta manera, dos instrucciones pueden estar en cada etapa de la canalización en cada ciclo. Obviamente, esto da como resultado una mayor complejidad de diseño a medida que se duplica el hardware; sin embargo, ofrece excelentes posibilidades de escalado de rendimiento.

Sin embargo, el aumento de rendimiento del aumento de las canalizaciones solo se escala hasta ahora de manera eficiente. Las restricciones térmicas y de tamaño imponen algunos límites. También hay importantes complicaciones de programación. Un despachador eficiente ahora es aún más crítico, ya que tiene que garantizar que ninguno de los dos conjuntos de instrucciones se base en el resultado de cualquiera de las otras instrucciones que se procesan.

Un predictor de rama es una parte del despachador que se vuelve cada vez más crítica cuanto más superescalar es un procesador. Algunas instrucciones pueden tener dos posibles resultados, cada uno de los cuales conduce a diferentes instrucciones de seguimiento. Un ejemplo simple sería una declaración "si". “Si esto es verdad haz aquello, de lo contrario haz esto otro”. Un predictor de bifurcación intenta predecir el resultado de una operación de bifurcación. Luego programa y ejecuta las instrucciones de manera preventiva siguiendo lo que cree que es el resultado probable.

Hay una gran cantidad de lógica compleja en los predictores de bifurcación modernos, que pueden resultar en tasas de éxito de predicción de bifurcación del orden del 98%. Una predicción correcta ahorra el tiempo que podría haberse desperdiciado esperando el resultado real, una predicción incorrecta requiere que la predicción instrucciones y cualquiera de sus resultados se descartan y las verdaderas instrucciones se ejecutan en su lugar, lo que viene con una pequeña penalización por tener solo esperó Por lo tanto, las altas tasas de éxito de la predicción pueden aumentar notablemente el rendimiento.

Conclusión

Un procesador de computadora se considera superescalar si puede realizar más de una instrucción por ciclo de reloj. Las primeras computadoras eran completamente secuenciales, ejecutando solo una instrucción a la vez. Esto significaba que cada instrucción tardaba más de un ciclo en completarse, por lo que estos procesadores eran subescalares. Una canalización básica que permite la utilización del hardware específico de la etapa para cada etapa de una instrucción puede ejecutar como máximo una instrucción por ciclo de reloj, lo que la hace escalar.

Cabe señalar que ninguna instrucción individual se procesa completamente en un solo ciclo de reloj. Todavía toma por lo menos cinco ciclos. Sin embargo, varias instrucciones pueden estar en proceso a la vez. Esto permite un rendimiento de una o más instrucciones completadas por ciclo.

Superescalar no debe confundirse con hiperescalador, que se refiere a empresas que pueden ofrecer recursos informáticos a hiperescala. La computación a hiperescala incluye la capacidad de escalar sin problemas recursos de hardware, como cómputo, memoria, ancho de banda de red y almacenamiento, según la demanda. Esto se encuentra típicamente en grandes centros de datos y entornos de computación en la nube.